Why This Matters for DDR Labs

Introspect Technology recently outlined the core steps they follow to probe DDR and LPDDR signals reliably—especially with LPDDR6 on the horizon. Their article reinforces what we see across Indian memory validation programs: clean probing dictates whether you meet timing margins and qualify modules on schedule. Below is our condensed take on their guidance, plus a few lessons from working alongside Teledyne LeCroy and Introspect deployments in production labs.

Plan the Interface Before Soldering

- Pick accessible lanes: Identify the byte lanes and command/address nets you must monitor. Introspect stresses adding breakout pads during PCB design so you can solder high-bandwidth tips without cutting traces later.

- Budget for length matching: Keep probe lead length to a minimum and match coax runs to avoid skew. For LPDDR6 rates, every millimetre of mismatch adds jitter that eats into noise margins.

- Document your reference points: Track which pads correspond to DQ, DQS, CA, and CK so future technicians can rebuild the setup without trial and error.

Use Remote Sampling Heads Wisely

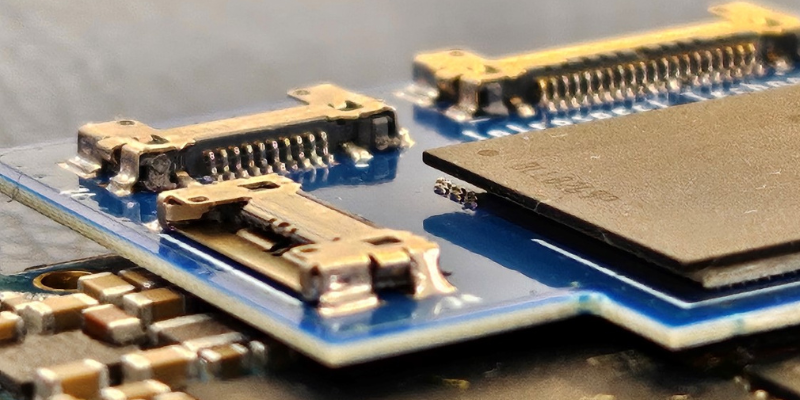

Like in their RSH2 smartphone example, Introspect shows how remote heads keep the active circuitry at the DUT and send conditioned signals back to the oscilloscope. On memory buses this delivers two big wins:

- Lower loading: Active probes present high impedance, letting you observe command/address swings as JEDEC intended.

- Cleaner fixtures: The remote head clamps near the package, so you only route short SMPM or coax jumpers to the scope.

Primeasure often pairs Introspect heads with Teledyne LeCroy oscilloscopes and protocol analyzers so engineers can correlate signal integrity and JEDEC compliance captures in the same run.

Oscilloscope Setup Checklist

- Deskew DQ and DQS: Always run the oscilloscope’s deskew routine after repositioning the probes. This ensures precise timing for eye diagrams and jitter analysis.

- Trigger on training patterns: Capture read/write levelling or training bursts to validate initialization before hitting full-speed traffic.

- Log reference captures: Save golden waveform overlays for each board revision. Introspect recommends these for spotting drifts caused by rework or new memory vendors.

- Automate reporting: Generate template-driven PDFs/CSV outputs so memory teams and OEM customers share a common view of pass/fail results.

Troubleshooting Tips from the Field

Introspect highlights that probing issues often masquerade as timing violations. When we see unexpected eye closure, we run through this triage list:

- Inspect solder joints for lifted pads or excess solder that adds inductance.

- Validate ground returns—LPDDR routing is dense, so neglected grounds introduce crosstalk quickly.

- Swap probe heads across channels to rule out damaged tips or cables.

- Capture power rail noise; many “mystery” DDR problems track back to PDN dips during bursts.

Source Inspiration

This summary draws on Introspect Technology’s post, “Probing DDR and LPDDR Signals”. Review their original article for imagery, fixture photos, and the latest LPDDR6 roadmap insights.

Need Help Instrumenting DDR or LPDDR Labs?

Primeasure supplies Introspect probing solutions and Teledyne LeCroy oscilloscopes across India. We can help design fixtures, automate compliance runs, and train teams on next-gen JEDEC standards.

Connect with Our Memory Experts